€1979 Fairchild Camera & Instrument Corporation 464 Ellis Street • Mountain View, California 94042 415/962-5011 • TWX 910-379-6435

## Introduction

This is an introductory brochure for Fairchild Advanced Schottky TTL, FAST, a family of TTL circuits that exhibits a combination of performance and efficiency unapproached by any other TTL family. Made with the proven Isoplanar process, 54F/74F circuits offer the switching speed and output drive capability of Schottky TTL, with superior noise margins and only one-fourth the power consumption.

Section 1 Product Index/Availability Gulde

Lists 54F/74F circuits currently planned, together

with their scheduled introduction dates. More

circuits will be added as market needs are identified.

#### Section 2 Family Characteristics

Discusses FAST circuit characteristics and noise margins and contains family ratings, dc specifications and ac waveforms.

#### Section 3 Circuit Selection Guides

Contains pinouts, features and functional descriptions; circuits are grouped functionally rather than numerically.

#### Section 4 Data Sheets

Contains full data sheets for SSI gates and flip-flops.

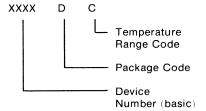

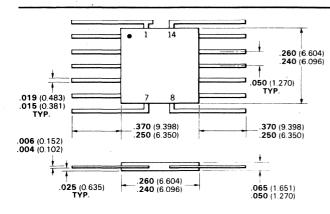

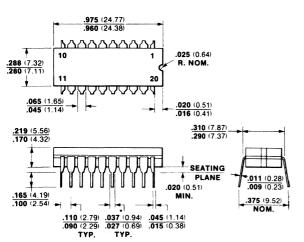

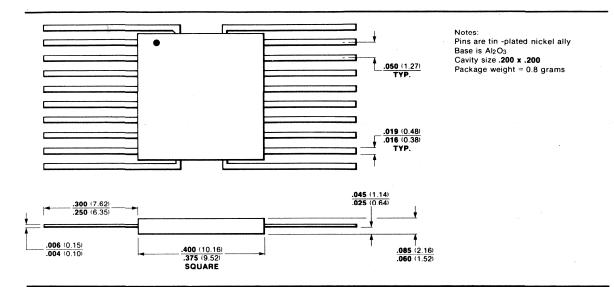

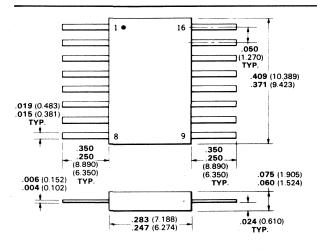

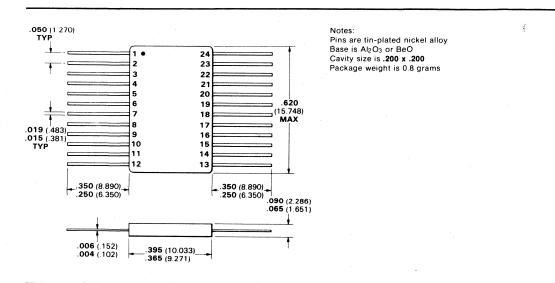

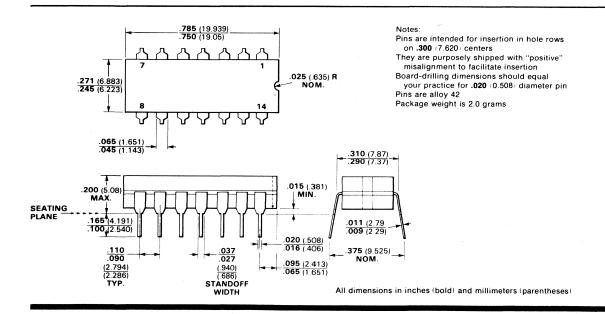

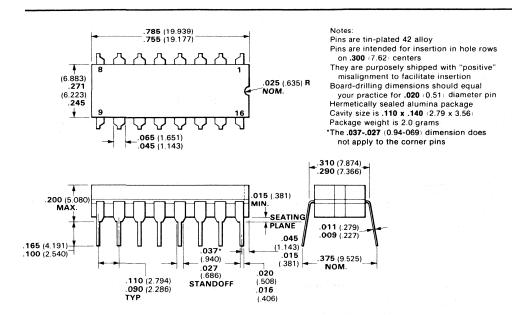

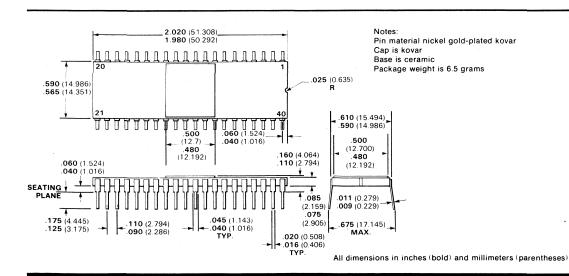

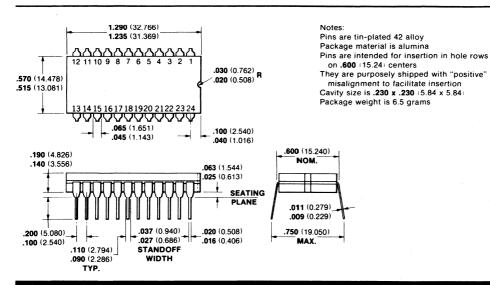

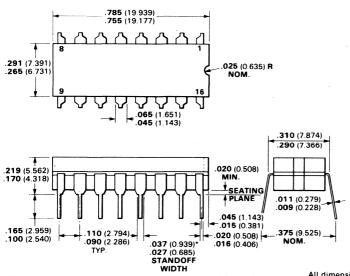

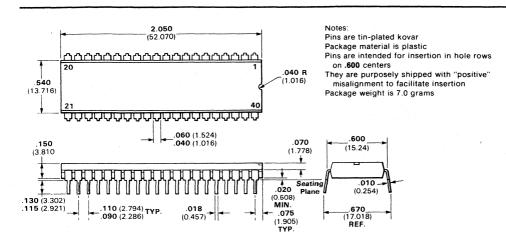

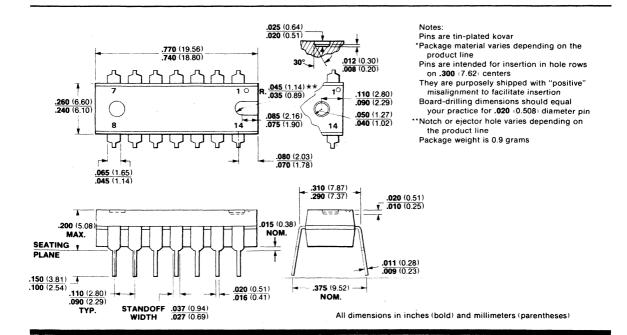

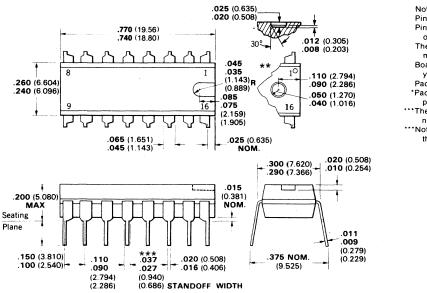

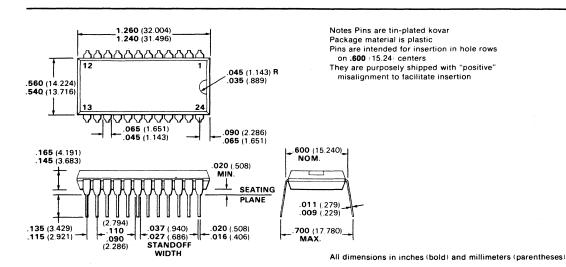

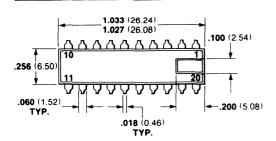

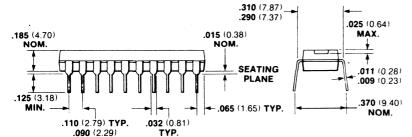

Section 5 Ordering Information and Package Outlines The simplified purchasing code which identifies not only the device type, but also the package type and temperature range, is explained. Detailed physical dimension drawings for each package are given.

Section 6 Field Sales Offices, Representatives and Distributor Locations

## **Table of Contents**

| Section 1        | Product Index/Availability Guide                         | 1-3  |

|------------------|----------------------------------------------------------|------|

| Section 2        | Family Characteristics                                   |      |

| <b>FAST Tech</b> | nnology                                                  | 2-3  |

| <b>FAST Circ</b> | uitry                                                    | 2-4  |

| Unit Loads       | s (U.L.)                                                 | 2-8  |

| Absolute N       | Maximum Ratings                                          | 2-9  |

| Recommen         | nded Operating Conditions                                | 2-9  |

| DC Charac        | cteristics Table                                         | 2-10 |

|                  | g and Waveforms                                          |      |

| Section 3        | Circuit Selection Guides                                 |      |

|                  |                                                          | 3-3  |

|                  |                                                          |      |

|                  |                                                          |      |

|                  | rs                                                       |      |

|                  | Demultiplexers                                           |      |

| Registers .      |                                                          | 3-16 |

| Counters .       |                                                          | 3-19 |

| Buffers/Tra      | ansceivers                                               | 3-22 |

| Arithmetic       | Operators                                                | 3-25 |

| Memories         |                                                          | 3-30 |

| Section 4        | Data Sheets                                              | 4-3  |

| Section 5        | Ordering Information and Package Outlines                |      |

|                  | nformation                                               | 5-3  |

| _                | Outlines                                                 |      |

| Section 6        | Sales Offices, Representatives and Distributor Locations | 6-3  |

## Section 1

## Product Index/ Availability Guide

| Device No.         | Description                                   | Availability | Page No.  |

|--------------------|-----------------------------------------------|--------------|-----------|

| 54F/74F00          | Quad 2-Input NAND Gate                        | Now          | 3-3, 4-3  |

| 54F/74F02          | Quad 2-Input NOR Gate                         | Now          | 3-3. 4-4  |

| 54F/74F04          | Hex Inverter                                  | Now          | 3-3, 4-5  |

| 54F/74F08          | Quad 2-Input AND Gate                         | Now          | 3-3, 4-6  |

| 54F/74F10          | Triple 3-Input NAND Gate                      | 2nd Qtr '79  | 3-3, 4-7  |

| 347/147 10         | Triple 3-iliput NAND Gate                     | 211d Qti 79  | 5-5, 4-7  |

| 54F/74F11          | Triple 3-Input AND Gate                       | 2nd Qtr '79  | 3-3, 4-8  |

| 54F/74F20          | Dual 4-Input NAND Gate                        | 3rd Qtr '79  | 3-4, 4-9  |

| 54F/74F32          | Quad 2-Input OR Gate                          | Now          | 3-4, 4-10 |

| 54F/74F64          | AND/OR-Invert Gate                            | 3rd Qtr '79  | 3-4, 4-11 |

| 54F/74F74          | Dual D-Type Positive Edge-Triggered Flip-Flop | 2nd Qtr '79  | 3-5, 4-12 |

| 54F/74F109         | Dual JK Positive Edge-Triggered Flip-Flop     | 2nd Qtr '79  | 3-5, 4-14 |

| 54F/74F151         | 8-Input Multiplexer                           | Now          | 3-9       |

| 54F/74F153         | Dual 4-Input Multiplexer                      | Now          | 3-9       |

| 54F/74F157         | Quad 2-Input Multiplexer                      | Now          | 3-10      |

|                    |                                               | Now          | 3-10      |

| 54F/74F158         | Quad 2-Input Multiplexer                      | NOW          | 3-10      |

| 54F/74F160         | Synchronous Presettable BCD Decade Counter    | 2nd Qtr '79  | 3-19      |

| 54F/74F161         | Synchronous Presettable Binary Counter        | 2nd Qtr '79  | 3-19      |

| 54F/74F162         | Synchronous Presettable BCD Decade Counter    | 2nd Qtr '79  | 3-19      |

| 54F/74F163         | Synchronous Presettable Binary Counter        | 2nd Qtr '79  | 3-19      |

| 54F/74F175         | Quad D Flip-Flop                              | 3rd Qtr '79  | 3-6       |

| <b>54F</b> //4F1/5 | Quad D Filp-Flop                              | 31d Qti 79   | 3-0       |

| 54F/74F181         | 4-Bit Arithmetic Logic Unit                   | Now          | 3-25      |

| 54F/74F182         | Carry Lookahead Generator                     | Now          | 3-25      |

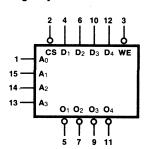

| 54F/74F189         | 64-Bit Random Access Memory                   | 3rd Qtr '79  | 3-30      |

| 54F/74F190         | Up/Down Decade Counter                        | 2nd Qtr '79  | 3-20      |

| 54F/74F191         | Up/Down Binary Counter                        | 2nd Qtr '79  | 3-20      |

| 341//41 131        | Op/Down Billary Counter                       | 2110 Qt. 70  | 0 20      |

| 54F/74F192         | Up/Down Decade Counter                        | 2nd Qtr '79  | 3-21      |

| 54F/74F193         | Up/Down Binary Counter                        | 2nd Qtr '79  | 3-21      |

| 54F/74F194         | 4-Bit Bidirectional Universal Shift Register  | 2nd Qtr '79  | 3-16      |

| 54F/74F240         | Octal Buffer/Line Driver                      | 3rd Qtr '79  | 3-22      |

| 54F/74F241         | Octal Buffer/Line Driver                      | 3rd Qtr '79  | 3-22      |

| E 4 E /7 4 E 0 4 0 | Quad Bus Transceiver                          | 3rd Qtr '79  | 3-23      |

| 54F/74F242         |                                               | 3rd Qtr '79  |           |

| 54F/74F243         | Quad Bus Transceiver                          |              | 3-23      |

| 54F/74F244         | Octal Buffer/Line Driver                      | 3rd Qtr '79  | 3-24      |

| 54F/74F251         | 8-Input Multiplexer                           | Now          | 3-11      |

| 54F/74F253         | Dual 4-Input Multiplexer                      | Now          | 3-11      |

| 54F/74F257         | Quad 2-Input Multiplexer                      | Now          | 3-12      |

| 54F/74F258         | Quad 2-Input Multiplexer                      | Now          | 3-12      |

| 54F/74F280         | 9-Bit Parity Generator/Checker                | 3rd Qtr '79  | 3-26      |

| 54F/74F283         | 4-Bit Binary Full Adder                       | 4th Qtr '79  | 3-26      |

| 54F/74F289         | 64-Bit Random Access Memory                   | 3rd Qtr '79  | 3-30      |

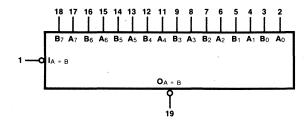

| 54F/74F299         | 8-Input Universal Shift/Storage Register      | 2nd Qtr '79  | 3-16      |

| 54F/74F322         | 8-Bit Serial/Parallel Register                | 2nd Qtr '79  | 3-16      |

|                    |                                               |              |           |

| 54F/74F323         | 8-Bit Universal Shift/Storage Register        | 2nd Qtr '79  | 3-17      |

| 54F/74F352         | Dual 4-Input Multiplexer                      | Now          | 3-13      |

| 54F/74F353         | Dual 4-Input Multiplexer                      | Now          | 3-13      |

|                    |                                               |              |           |

| Device No. | Description                                         | Availability | Page No |

|------------|-----------------------------------------------------|--------------|---------|

| 54F/74F373 | Octal Transparent Latch                             | 2nd Qtr '79  | 3-8     |

| 54F/74F374 | Octal D-Type Flip-Flop                              | 2nd Qtr '79  | 3-6     |

| 54F/74F379 | Quad Parallel Register                              | 3rd Qtr '79  | 3-7     |

| 54F/74F381 | 4-Bit Arithmetic Logic Unit                         | 2nd Qtr '79  | 3-27    |

| 54F/74F382 | 4-Bit Arithmetic Logic Unit                         | 2nd Qtr '79  | 3-27    |

| 54F/74F398 | Quad 2-Port Register                                | 3rd Qtr '79  | 3-18    |

| 54F/74F399 | Quad 2-Port Register                                | 3rd Qtr '79  | 3-18    |

| 54F/74F521 | 8-Bit Identity Comparator                           | 3rd Qtr '79  | 3-28    |

| 54F/74F533 | Octal Transparent Latch                             | 3rd Qtr '79  | 3-8     |

| 54F/74F534 | Octal D-Type Flip-Flop                              | 3rd Qtr '79  | 3-7     |

| 54F/74F537 | 1-of-10 Decoder                                     | 2nd Qtr '79  | 3-14    |

| 54F/74F538 | 1-of-8 Decoder                                      | 2nd Qtr '79  | 3-14    |

| 54F/74F539 | Dual 1-of-4 Decoder                                 | 2nd Qtr '79  | 3-15    |

| 54F/74F545 | Octal Bidirectional Transceiver                     | 3rd Qtr '79  | 3-24    |

| 54F/74F558 | 8-Bit by 8-Bit Multiplier                           | 3rd Qtr '79  | 3-28    |

| 54F/74F559 | Expandable 8-Bit Twos Complement Multiplier/Divider | 3rd Qtr '79  | 3-29    |

|                              | Product Index/Availability Guide                         | 1 |

|------------------------------|----------------------------------------------------------|---|

| Family Characteristics       | <b>→</b>                                                 | 2 |

|                              | Circuit Selection Guides                                 | 3 |

| F 1026 400 C 5th 3 48.55.00M | Data Sheets                                              | 4 |

|                              | Ordering Information and Package Outlines                | 5 |

|                              | Sales Offices, Representatives and Distributor Locations | 6 |

## Section 2

## **Circuit Characteristics**

#### **FAST Technology**

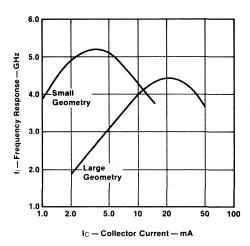

FAST is an acronym for Fairchild Advanced Schottky TTL. FAST circuits are made with the advanced Isoplanar II process, which produces transistors with very high, well-controlled switching speeds, extremely small parasitic capacitances and f⊺ in excess of 5 GHz. Isoplanar is an established Fairchild process, used for years in the manufacture of bipolar memories, CMOS, subnanosecond ECL and I³L™ (Isoplanar Intergrated Injection Logic) LSI devices.

In the Isoplanar process, components are isolated by a selectively grown thick oxide rather than the P+ isolation region used in the Planar process. Since this oxide needs no separation from the base-collector regions, component and chip sizes are substantially reduced. The base and emitter ends terminate in the oxide wall; masks can thus overlap the device area into the isolation oxide. This overlap feature eliminates the extremely close tolerances normally required for base and emitter masking, and the standard photolithographic processes can be used.

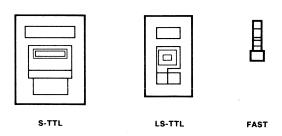

Fig. 2-1 Relative Transistor Size in Various TTL Families

Figure 2-1 shows the relative size of phase-splitter transistors (Q2 in Figure 2-3) used in Schottky, Low Power Schottky and FAST circuits. The LS-TTL transistor is smaller than that of S-TTL because of process refinements, shallower diffusions and smaller operating currents. The relative size of the FAST transistor illustrates the remarkable reduction afforded by the Isoplanar process. This in turn reduces junction capacitances, while the oxide isolation reduces side-wall capacitance. The effect of these reductions is an increase in frequency response by a factor of three or more. Figure 2-2 shows the frequency response of two sizes of transistors made with the Isoplanar II process. Because they have modest, well-defined loads and thus can use smaller, faster transistors, internal gates of MSI devices are faster than SSI gates such as the 74F00 or 74F02. SSI gates, on the other hand, are designed to have high output drive capability and thus use larger transistors.

Fig. 2-2 Isoplanar Transistor Frequency Response

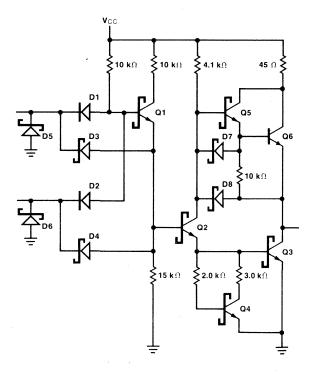

#### **FAST Circuitry**

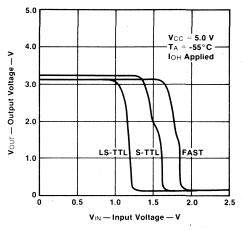

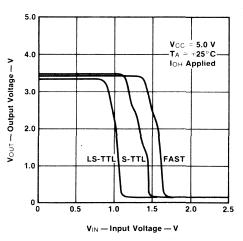

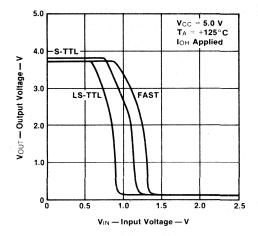

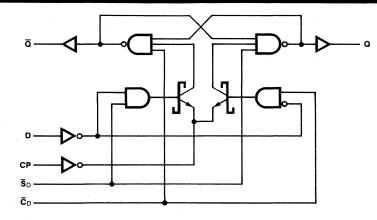

The 2-input NAND gate, shown in Figure 2-3, has three stages of gain (Q1, Q2, Q3) instead of two stages as in other TTL families. This raises the input threshold voltage and increases the output drive. The higher threshold makes it possible to use pn diodes for the input AND function (D1 and D2) and still achieve an input threshold of 1.5 V. The capacitance of these diodes is comparatively low, which results in improved ac noise immunity. The effect of the threshold adjustment can be seen in the voltage transfer characteristics of Figures 2-4, 2-5 and 2-6. At 25°C (Figure 2-5) the FAST circuit threshold is nearly centered between the 0.8 V and 2.0 V limits specified for TTL circuits. This gives a better balance between the HIGH- and LOW-state noise margins. The +125°C characteristics (Figure 2-6) show that the FAST circuit threshold is comfortably above the 0.8 V specification, more so than in S-TTL or LS-TTL circuits. At -55°C, the FAST circuit threshold is still well below the 2.0 V specification, as shown in Figure 2-4.

Fig. 2-3 Basic FAST Gate Schematic

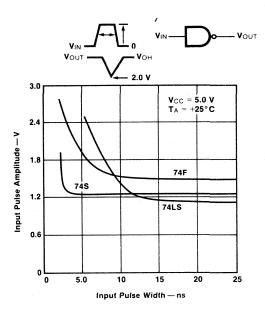

The effect of the FAST circuit threshold placement is shown in the pulse noise immunity curves of Figure 2-7. These characteristics were determined by measuring the various combinations of input pulse and duration required to cause the gate output to fall to the 2.0 V level. The higher threshold of FAST circuits gives them a clear advantage in noise immunity over S-TTL and LS-TTL circuits.

Fig. 2-4 Transfer Functions at Low Temperature

Fig. 2-5 Transfer Functions at Room Temperature

FAST circuits contain several speed-up diodes to help discharge internal capacitances. Referring again to Figure 2-3, when a HIGH-to-LOW transition occurs at the D1 input, for example, Schottky diode D3 acts as a low-resistance path to discharge the several parasitic capacitances connected to the base of Q2. This effect only comes into play, however, as the input signal falls below about 1.2 V; D3 does not act as an entry path for negative spikes superimposed on a HIGH input level. When Q2 turns on and its collector voltage falls, D7 provides a discharge path for capacitance at the base of Q6. Whereas D3, D4 and D7 enhance switching speed by helping to discharge internal nodes, D8 contributes to the ability of a FAST circuit to rapidly discharge load capacitance. Part of the charge stored in load capacitance passes through D8 and Q2 to increase the base current of Q3 and increase Q3's current sinking capability during the HIGH-to-LOW output voltage transition.

Fig. 2-6 Transfer Functions at High Temperature

Fig. 2-7 Pulse Noise Immunity Comparison

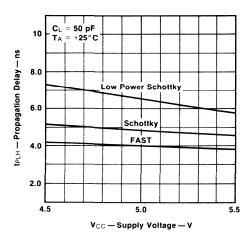

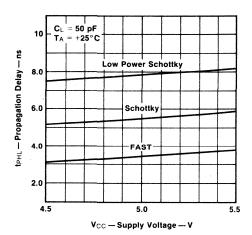

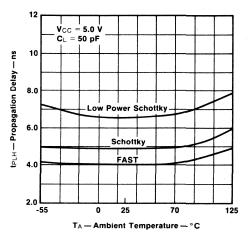

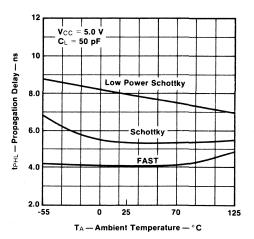

The Schottky clamping diodes built into the transistors prevent saturation, thereby eliminating storage time as a factor in switching speed. Similarily, the speed-up diodes tend to minimize the impact of other variables on switching speed. The overall effect is to minimize variation in switching speed of FAST circuits with variations in supply voltage and ambient temperature (Figures 2-8 through 2-11). Propagation delay is specified not only under nominal supply voltage and temperature conditions, but also over the recommended operating range of Vcc and TA for both military and commercial grade devices.

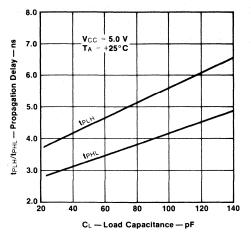

The internal switching speed of a logic circuit is only one aspect of the circuit's suitability for high-speed operation at the system or subsystem level; the other aspect is the ability of the circuit to drive load capacitance. FAST circuit outputs are structured to sink at least 20 mA in the LOW state, the same as S-TTL. This capability plus the effect of the aforementioned feedback through D8 assures that the circuit can rapidly discharge capacitance. During a LOW-to-HIGH transition, the pull-up current is limited by the 45  $\Omega$  resistor, versus 55  $\Omega$  for S-TTL.

Fig. 2-8 Propagation Delay tPLH vs VCC

Fig. 2-9 Propagation Delay tPHL vs VCC

Fig. 2-10 Propagation Delay tPLH vs Temperature

Fig. 2-11 Propagation Delay tPHL vs Temperature

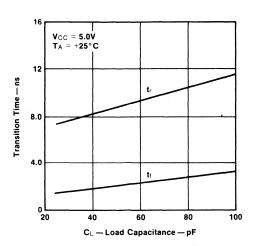

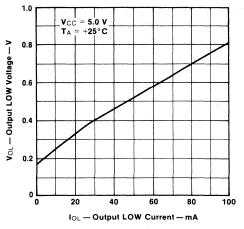

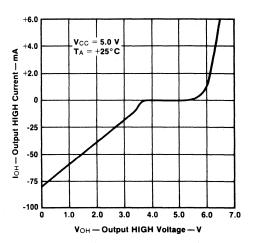

Therefore, FAST circuits are inherently more capable than S-TTL of charging load capacitance. Figures 2-12 and 2-13 indicate the effect of load capacitance on propagation delays and transition times of FAST circuits. Figure 2-14 shows the typical output LOW voltage Vol as a function of load current. The typical I-V characteristic in the quiescent HIGH state is shown in Figure 2-15. In the lower left, the intercept along the vertical axis indicates the short-circuit output current los. From this point to approximately -10 mA, the slope is

about 50  $\Omega$ , indicating that the totem-pole pull-up is saturated and current is limited principally by the 45  $\Omega$  resistor. From -10 mA upward almost to the horizontal axis, the slope is the dynamic output resistance of transistor Q6. That part of the characteristic in the upper right shows that a bi-state output cannot be pulled up much above Vcc because of the sneak path through D8 and the 4.1 k $\Omega$  resistor back to Vcc.

Fig. 2-12 Propagation Delay vs Load Capacitance

Fig. 2-13 Transition Time vs Load Capacitance

Fig. 2-14 Output LOW Characteristic

Fig. 2-15 Output HIGH Characteristic

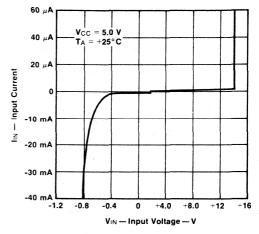

A typical input I-V characteristic is shown in Figure 2-16. An input clamping diode (D5 or D6 in Figure 2-3) conducts if an input signal tends to go more negative than about -0.4 V. This limits the undershoot that might occur at the end of a long line following a HIGH-to-LOW transition. The clamping diodes in FAST circuits have been improved over those used in LS-TTL to prevent parasitic coupling through sneak paths to other components on the chip. For input voltage in the range of -0.4 V to about +1.5 V, the input current is governed principally by the 10 k $\Omega$  pull-up resistor of the input gate. With VCC at the recommended maximum (+5.5 V or +5.25 V) and the input at +0.4 V, the specified maximum input current is 0.6 mA. This compares favorably with the 0.4 mA specified maximum for LS-TTL and is far below the 2.0 mA maximum for an S-TTL input. Thus, in a system comprised of FAST devices, there is less need for buffering to increase fan-out.

Fig. 2-16 Input Characteristic

#### Unit Loads (U.L.)

For convenience in system design, the input loading and fan-out characteristics of each circuit are specified in terms of unit loads. One unit load in the HIGH state is defined as 40 µA; thus both the input HIGH leakage current IIH and the output HIGH current-sourcing capability IOH are normalized to 40 µA. The specified maximum lin for a standard FAST input is 20 uA, or 0.5 U.L., while the IOH rating for a standard output is 1.0 mA, or 25 U.L. Similarly, one unit load in the LOW state is defined as 1.6 mA and both the input LOW current IIL and the output LOW current-sinking capability IOL are normalized to 1.6 mA. The specified maximum liL for a standard FAST input is 0.6 mA, or 0.375 U.L., while the local rating for a standard output is 20 mA, or 12.5 U.L. On the data sheets, the input and output load factors are listed in the Input Loading/Fan-Out Table. The table from the 54F/74F04 Hex Inverter is reproduced below.

In the right-hand column the input HIGH/LOW load factors are 0.5/0.375, with the first number representing IIH and the second representing IIL. For testing or procurement purposes, these load factors can easily be translated to actual test limits by multiplying them by 40  $\mu A$  and 1.6 mA, respectively. The second set of numbers represents the rated output HIGH/LOW load currents IOH and IOL, respectively. The indicated HIGH/LOW drive factors of 25/12.5 translate to 1.0 mA and 20 mA by multiplying them by 40  $\mu A$  and 1.6 mA, respectively.

#### INPUT LOADING/FAN-OUT: See Section 2 for U.L. definitions

| PIN NAMES | DESCRIPTION       | <b>54F/74F</b><br>HIGH/LOW |

|-----------|-------------------|----------------------------|

|           | Inputs<br>Outputs | 0.5/0.375<br>25/12.5       |

#### Absolute Maximum Ratings1

(beyond which useful life may be impaired)

| Storage Temperature             | -65°C to +150°C     |

|---------------------------------|---------------------|

| Ambient Temperature under Bias  | -55°C to +125°C     |

| Junction Temperature under Bias | -55°C to +175°C     |

| Vcc Pin Potential to Ground Pin | -0.5 V to +7.0 V    |

| Input Voltage <sup>2</sup>      | -0.5 V to +7.0 V    |

| Input Current <sup>2</sup>      | -30 mA to +5.0 mA   |

| Voltage Applied to Output in    |                     |

| HIGH State:                     |                     |

| Standard Output                 | -0.5 V to Vcc Value |

| 3-State Output (with Vcc = 0 V) | -0.5 V to +5.5 V    |

| Current Applied to Output in    | twice the rated loa |

| LOW State (Max)                 | times the rated top |

#### Recommended Operating Conditions<sup>1</sup>

|                                                                  | Min               | Max               |

|------------------------------------------------------------------|-------------------|-------------------|

| Free Air Ambient Temperature<br>Military (XM)<br>Commercial (XC) | -55°C<br>0°C      | +125° C<br>+70° C |

| Supply Voltage<br>Military (XM)<br>Commercial (XC)               | +4.5 V<br>+4.75 V | +5.5 V<br>+5.25 V |

- 1. Unless otherwise restricted or extended by detail specifications.

- 2. Either input voltage or current limit sufficient to protect inputs.

#### 54F/74F FAMILY DC CHARACTERISTICS1

| SYMBOL           | PARAMETER                           |                                     | LIMITS2           |                   | UNITS                     | Vcc4 | CONDITIONS <sup>2</sup> |                                                                                                           |

|------------------|-------------------------------------|-------------------------------------|-------------------|-------------------|---------------------------|------|-------------------------|-----------------------------------------------------------------------------------------------------------|

| OT MIDOL         |                                     |                                     | Min               | Тур3              | Max                       | ONT  | <b>V</b> CC.            | CONDITIONS                                                                                                |

| ViH              | Input HIGH Volta                    | age                                 | 2.0               |                   |                           | V    |                         | Recognized as a HIGH<br>Signal Over Recommended<br>Vcc and TA Range                                       |

| VIL              | Input LOW Volta                     | ge                                  |                   |                   | 0.8                       | ٧    |                         | Recognized as a LOW<br>Signal Over Recommended<br>Vcc and T <sub>A</sub> Range                            |

| VcD              | Input Clamp Dio                     | de Voltage                          |                   |                   | -1.2                      | V    | Min                     | I <sub>IN</sub> = -18 mA                                                                                  |

| Vон              | Output<br>HIGH Voltage              | Std.6 Mil.<br>Std.6 Com.<br>3-State | 2.5<br>2.7<br>2.4 | 3.4<br>3.4<br>3.2 |                           | V    | Min                     | $I_{OH} = 40 \mu A$ Multiplied<br>by Output HIGH U.L.<br>Shown on Data Sheet                              |

| VoL              | Output LOW Voltage                  |                                     |                   | 0.35              | 0.5                       | ٧    | Min                     | I <sub>OL</sub> = 1.6 mA Multiplied<br>by Output LOW U.L.<br>Shown on Data Sheet                          |

| hн               | Input HIGH Curr                     | 0.5 U.L.<br>1.0 U.L.<br>n U.L.      |                   |                   | 20<br>40<br>n(40)         | μΑ   | Max                     | I <sub>IH</sub> = 40 μA Multiplied by<br>Input HIGH U.L. Shown on<br>Data Sheet; V <sub>IN</sub> = 2.7 V  |

|                  | Input High Curre<br>Breakdown Test, |                                     |                   |                   | 100                       | μΑ   | Max                     | V <sub>IN</sub> = 7.0 V                                                                                   |

| hL               | Input LOW<br>Current                | 0.375 U.L.<br>0.75 U.L.<br>n U.L.   |                   |                   | -0.6<br>-1.2 ,<br>n(-1.6) | mA   | Max                     | I <sub>IL</sub> = -1.6 mA Multiplied by<br>Input LOW U.L. Shown on<br>Data Sheet; V <sub>IN</sub> = 0.5 V |

| Іохн             | 3-State Output O<br>Current HIGH    | )FF                                 |                   |                   | 20                        | μΑ   | Max                     | V <sub>OUT</sub> = 2.4 V                                                                                  |

| lozL,            | 3-State Output O<br>Current LOW     | )FF                                 |                   |                   | -20                       | μΑ   | Max                     | Vουτ = 0.5 V                                                                                              |

| los <sup>5</sup> | Output Short-                       | Standard <sup>6</sup> /<br>3-State  | -60               |                   | -150                      | mA   | Max                     | V <sub>О</sub> = 0 V                                                                                      |

|                  | Circuit Current                     | Buffers/<br>Line Dvrs               | -100              |                   | -225                      |      |                         |                                                                                                           |

<sup>1.</sup> Unless otherwise noted, conditions and limits apply throughout the temperature range for which the particular device type is rated. The ground pin is the reference level for all applied and resultant voltages.

<sup>2.</sup> Unless otherwise stated on individual data sheets.

<sup>3.</sup> Typical characteristics refer to  $T_A = +25^{\circ}C$  and  $V_{CC} = +5.0$  V.

<sup>4.</sup> Min and Max refer to the values listed in the table of recommended operating conditions.

<sup>5.</sup> For testing los, the use of high-speed test apparatus and/or sample-and-hold techniques are preferable in order to minimize internal heating and more accurately reflect operational values. Otherwise, prolonged shorting of a HIGH output may raise the chip temperature well above normal and thereby cause invalid readings in other parameter tests. In any sequence of parameter tests, los tests should be performed last.

<sup>6.</sup> Standard refers to the totem-pole pull-up circuitry commonly used for the particular family, as distinguished from buffers, line drivers or 3-state outputs.

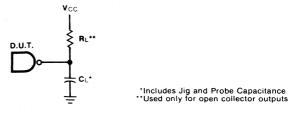

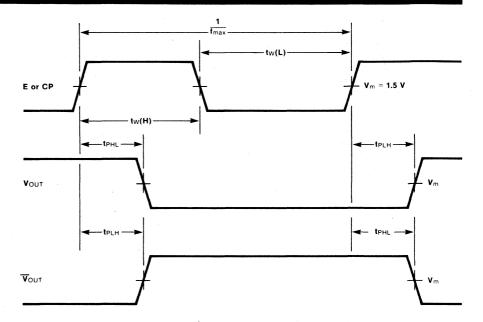

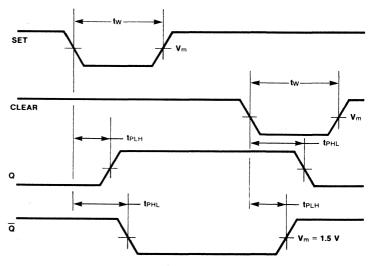

#### **AC Loading and Waveforms**

Figure 2-17 shows the load circuit configuration used for ac testing of bi-state outputs. The appropriate value of  $C_L$  is shown on each individual data sheet in the ac table column headings. A pulse generator signal swing of 0 V to  $\pm 3.0$  V, terminated at the test socket, is recommended for ac testing. A 1.0 MHz square wave is recommended for most propagation delay tests, with rise and fall times of 2.5 ns. The generator pulse repetition rate must necessarily be increased for testing  $f_{max}$ . Two pulse generators are usually required for testing such parameters as set-up time, hold time, recovery time, etc. Low inductance type load capacitors are recommended for best correlation with factory test results.

Fig. 2-17 Test Load for Bi-State Mode

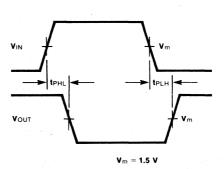

Fig. 2-18 Waveform for Inverting Functions

Fig. 2-19 Waveform for Non-Inverting Functions

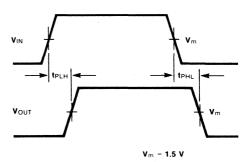

Fig. 2-20 Set-up and Hold Times, Rising-Edge Clock

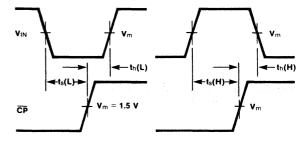

Fig. 2-21 Propagation Delays from Rising-Edge Clock or Enable

Fig. 2-22 Propagation Delays from Set and Clear (or Reset)

|                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                | Product Index/Availability Guide                         | 1 |

|--------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------|----------------------------------------------------------|---|

|                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                | Family Characteristics                                   | 2 |

| Circuit Selection Guides                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                       | <b>→</b>                                                 | 3 |

|                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                | Data Sheets                                              | 4 |

| The state of the s | Ordering Information and Package Outlines                | 5 |

|                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                | Sales Offices, Representatives and Distributor Locations | 6 |

Para Parc

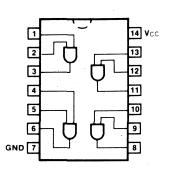

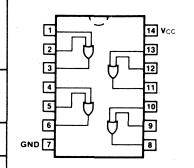

54F/74F02 Quad 2-Input NOR Gate 54F/74F04 Hex Inverter

## 54F/74F08 Quad 2-Input AND Gate

**54F/74F10**Triple 3-Input NAND Gate

**54F/74F11**Triple 3-Input AND Gate

54F/74F20 Dual 4-Input NAND Gate 54F/74F32 Quad 2-Input OR Gate 54F/74F64 AND OR-Invert Gate

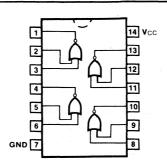

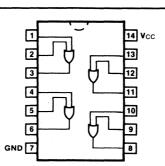

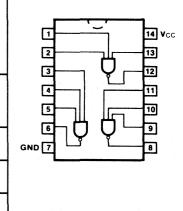

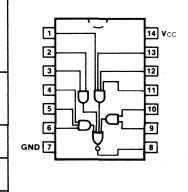

## Dual D-Type Positive Edge-Triggered Flip-Flop

54F/74F74

**Description** — The 'F74 is a dual D-type flip-flop with Direct Clear and Set inputs and complementary (Q,  $\overline{Q}$ ) outputs. Information at the input is transferred to the outputs on the positive edge of the clock pulse. Clock triggering occurs at a voltage level of the clock pulse and is not directly related to the transition time of the positive-going pulse. The D input can change when the clock is in either state without affecting the flip-flop, provided that the D signal is in the desired state during the recommended setup and hold times relative to the rising edge of the clock. A LOW signal on  $\overline{S}_D$  or  $\overline{C}_D$  prevents clocking and forces Q or  $\overline{Q}$  HIGH, respectively. Simultaneous LOW signals on  $\overline{C}_D$  and  $\overline{S}_D$  force both Q and  $\overline{Q}$  HIGH.

Buffered Outputs

Fully Edge-Triggered

Overriding Direct Set and Clear

Clock Frequency 145 MHz Typ

Propagation Delay 4.8 ns Typ

Supply Current 10.5 mA Typ

# 2 — D<sub>1</sub> S<sub>D1</sub> S<sub>D2</sub> D<sub>2</sub> S<sub>D2</sub> Q<sub>2</sub> 9 3 — CP<sub>1</sub> 11 CP<sub>2</sub> Q<sub>2</sub> C<sub>D2</sub> 0 8

V<sub>CC</sub> = Pin 14 GND = Pin 7

**Logic Symbol**

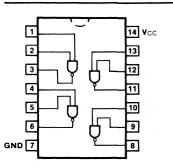

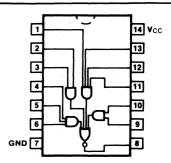

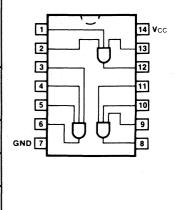

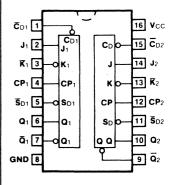

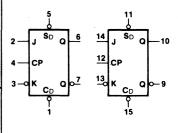

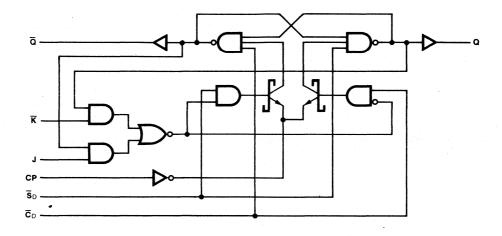

## Dual JK Positive Edge-Triggered Flip-Flop

54F/74F109

Description — The 'F109 contains two independent, high speed JK flip-flops with Direct Set and Clear inputs. Synchronous state changes are initiated by the rising edge of the clock. Triggering occurs at a voltage level of the clock and is not directly related to the transition time. The J and K inputs can change when the clock is in either state without affecting the flip-flop, provided that they are in the desired state during the recommended setup and hold times relative to the rising edge of the clock. A LOW signal on SD or CD prevents clocking and forces Q or Q HIGH, respectively. Simultaneous LOW signals on SD and CD force both Q and Q HIGH. A D input is available by tying J and K together.

Buffered Outputs

Fully Edge-Triggered

Overriding Direct Set and Clear

Clock Frequency 140 MHz Typ

Propagation Delay 4.8 ns Typ

Supply Current 11.7 mA Typ

#### Logic Symbol

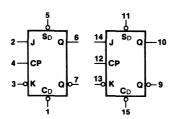

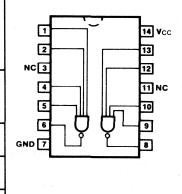

## Quad D Flip-Flop

## 54F/74F175

**Description** — The 'F175 contains four high speed, edge-triggered D flip-flops with common Clock and Master Reset inputs, and individual D inputs and Q and  $\overline{Q}$  outputs. Information on the D inputs is entered by the rising edge of the clock, provided that the recommended setup and hold times are observed. A LOW signal on  $\overline{MR}$  forces all Q outputs LOW and  $\overline{Q}$  outputs HIGH, independent of Clock or Data inputs.

True and Complement Outputs Fully Edge-Triggered Asynchronous Common Reset Clock Frequency 150 MHz Typ Propagation Delay 6.3 ns Typ Supply Current 21 mA Typ

#### Logic Symbol

V<sub>CC</sub> = Pin 16 GND = Pin 8

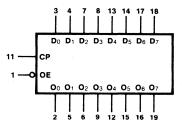

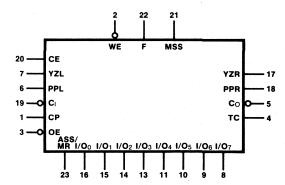

# Octal D-Type Flip-Flop

(With 3-State Outputs)

54F/74F374

**Description** — The 'F374 contains eight edge-triggered flip-flops with buffered 3-state outputs for bus oriented applications. Information on the D inputs is entered on the rising edge of the common Clock input, provided that the recommended setup and hold times are observed. A HIGH signal on the common Output Enable forces the outputs to the high impedance state but does not affect the state of the flip-flops or subsequent data entry.

Buffered 3-State Outputs

D-Type Inputs

Fully Edge-Triggered

Clock Frequency 110 MHz Typ

Propagation Delay 9.5 ns Typ

Supply Current 52 mA Typ

#### Logic Symbol

## Quad Parallel Register

54F/74F379

(With Enable)

**Description** — The 'F379 storage register contains four edge-triggered flip-flops with individual D inputs and Q and  $\overline{Q}$  outputs and with common Clock and input Enable inputs. Information present on the D inputs is entered on the rising edge of the clock, provided that  $\overline{E}$  is LOW and the recommended setup and hold times are observed. When the  $\overline{E}$  input is HIGH, the register retains the present data independent of the clock and D inputs.

Buffered Input Enable

Buffered Common Clock

Fully Edge-Triggered

Clock Frequency 150 MHz Typ

Propagation Delay 6.3 ns Typ

Supply Current 27 mA Typ

#### **Logic Symbol**

V<sub>CC</sub> = Pin 16 GND = Pin 8

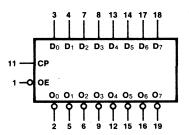

## Octal D-Type Flip-Flop

(With 3-State Outputs)

54F/74F534

**Description** — The 'F534 contains eight edge-triggered flip-flops with individual D inputs and  $\overline{Q}$  outputs, and with common Clock and 3-state Output Enable inputs. Information on the D inputs is entered on the rising edge of the clock, provided that the recommended setup and hold times are observed. A HIGH signal on  $\overline{OE}$  forces the outputs to the high impedance state but does not affect the state of the flip-flops or subsequent data entry. The 'F534 is the same as the 'F374 but with inverted outputs.

Inverted 3-State Outputs

D-Type Inputs

Fully Edge-Triggered

Clock Frequency 110 MHz Typ

Propagation Delay 9.5 ns Typ

Supply Current 52 mA Typ

#### **Logic Symbol**

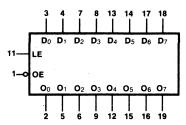

## Octal Transparent Latch

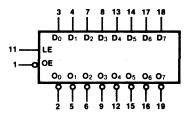

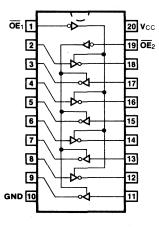

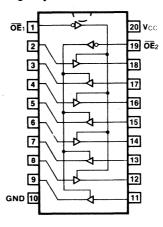

54F/74F373

(With 3-State Outputs)

**Description** — The 'F373 contains eight D-type latches with 3-state outputs for bus organized applications. When the common Latch Enable input is HIGH the latches are transparent, i.e. an output will change state each time its D input changes. When LE is LOW, the data that meets the recommended setup and hold times is latched. A HIGH signal on the common Output Enable input forces the outputs to the high impedance state but does not affect the state of the latches or subsequent data entry.

**Buffered 3-State Outputs D-Type Inputs** Transparent Latches Propagation Delay 6.0 ns Typ Supply Current 46 mA Typ

#### Logic Symbol

Vcc = Pin 20 GND = Pin 10

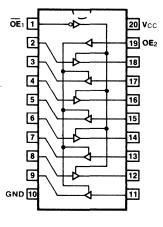

## Octal Transparent Latch 54F/74F533

(With 3-State Outputs)

**Description** — The 'F533 contains eight D-type latches with inverted 3-state outputs for bus organized applications. When the common Latch Enable input is HIGH the latches are transparent, i.e. an output will change state each time its D input changes. When LE is LOW, the data that meets the recommended setup and hold times is latched. A HIGH signal on the common Output Enable input forces the outputs to the high impedance state but does not affect the state of the latches or subsequent data entry. The 'F533 is the same as the 'F373 except that the outputs are inverted.

**Inverted 3-State Outputs D-Type Inputs Transparent Latches** Propagation Delay 8.0 ns Typ Supply Current 46 mA Typ

#### Logic Symbol

Vcc = Pin 20 GND = Pin 10

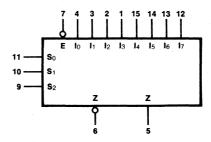

## 8-Input Multiplexer

## 54F/74F151

**Description** — The 'F151 is a high speed 8-input digital multiplexer with complementary outputs. It can select one line of data from up to eight sources. Signals on the Select inputs  $S_0-S_2$  determine which of the inputs is routed to the output. A LOW signal on the Enable input  $\overline{E}$  allows the Z output to follow the selected input. A HIGH on  $\overline{E}$  forces the Z output LOW and  $\overline{Z}$  HIGH.

Complementary Outputs Propagation Delay 6.3 and 8.1 ns Typ Supply Current 11 mA Typ

#### Logic Symbol

Vcc = Pin 16 GND = Pin 8

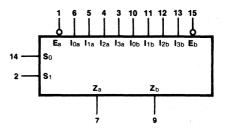

## Dual 4-Input Multiplexer

## 54F/74F153

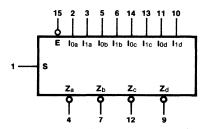

**Description** — The 'F153 contains two 4-input multiplexers with common Select inputs and separate Enable inputs. Signals applied to the Select inputs determine, within each section, which of the four data inputs is routed to the output. A LOW signal on an Enable input allows the output to follow the selected input. A HIGH signal on an Enable forces the output LOW.

Separate Enable Inputs Common Select Inputs Propagation Delay 7.9 ns Typ Supply Current 12 mA Typ

#### Logic Symbol

# Quad 2-Input Multiplexer

## 54F/74F157

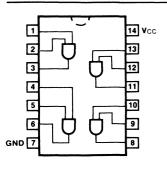

**Description** — The 'F157 contains four 2-input multiplexers with common Select and Enable inputs. It can select four bits of data from either of two sources. A LOW signal on the Enable input allows the selected data to be routed to the output. A HIGH signal on the Enable forces the outputs LOW.

Common Select Input Common Enable Input Propagation Delay 7.9 ns Typ Supply Current 15 mA Typ

#### **Logic Symbol**

V<sub>CC</sub> = Pin 16 GND = Pin 8

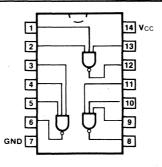

## Quad 2-Input Multiplexer

## 54F/74F158

**Description** — The 'F158 contains four 2-input multiplexers with common Select and Enable inputs and with inverting outputs. It selects four bits of data from either of two sources. A LOW signal on the Enable input allows the selected data to be routed to the outputs. A HIGH signal on the Enable forces the outputs HIGH.

Inverting Outputs Common Select Input Common Enable Input Propagation Delay 6.3 ns Typ Supply Current 10 mA Typ

#### **Logic Symbol**

## 8-Input Multiplexer

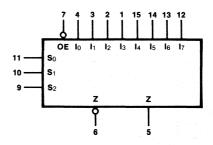

54F/74F251

(With 3-State Outputs)

**Description** — The 'F251 is a high speed 8-input multiplexer with complementary 3-state outputs. It provides the capability of selecting one line of data from up to eight sources, as determined by signals applied to the Select inputs S<sub>0</sub> — S<sub>2</sub>. A LOW signal on the Output Enable input  $\overline{OE}$  allows the Z output to follow the selected input. A HIGH signal on  $\overline{OE}$  forces both outputs to the high impedance state.

Complementary 3-State Outputs Propagation Delay 2.9 or 4.7 ns Typ Supply Current 10.5 mA Typ

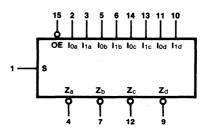

#### Logic Symbol

V<sub>CC</sub> = Pin 16 GND = Pin 8

## Dual 4-Input Multiplexer

(With 3-State Outputs)

54F/74F253

**Description** — The 'F253 contains two 4-input multiplexers with common Select inputs, separate Output Enable  $(\overline{OE})$  and 3-state outputs. Signals applied to the Select inputs determine, in each section, which of the four data inputs is routed to the output. A LOW signal on  $\overline{OE}$  allows the output to follow the selected input. A HIGH on  $\overline{OE}$  forces the output to the high impedance state. Outputs are thus capable of interfacing directly with bus oriented systems.

3-State Outputs Common Select Inputs Separate Enable Inputs Propagation Delay 4.5 ns Typ Supply Current 12.5 mA Typ

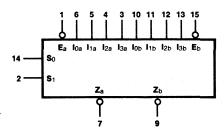

#### Logic Symbol

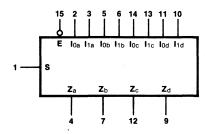

## Quad 2-Input Multiplexer

54F/74F257

(With 3-State Outputs)

Description — The 'F257 is a quad 2-input multiplexer with 3-state outputs. Four bits of data two sources can be selected using a Common Data Select input. The four outputs present the selected data in true (non-inverted) form. The outputs may be switched to a high impedance state with a HIGH on the common Output Enable (OE) input; therefore, the outputs can interface directly with bus oriented systems.

3-State Outputs **Common Select Input** Common Enable Input Propagation Delay 4.5 ns Typ Supply Current 14.6 mA Typ

#### **Logic Symbol**

Vcc = Pin 16 GND = Pin 8

## Quad 2-Input Multiplexer

(With 3-State Outputs)

54F/74F258

**Description** — The 'F258 is a quad 2-input multiplexer with 3-state outputs. Four bits of data from two sources can be selected using a common data select input. The four outputs present the selected data in the complement (inverted) form. The outputs may be switched to a high impedance state with a HIGH on the common Output Enable (OE) input; therefore, the outputs can interface directly with bus oriented systems. The 'F258 is the same as the 'F257 except that the outputs are inverted.

**Inverting 3-State Outputs Common Select Input** Common Enable Input Propagation Delay 2.9 ns Typ Supply Current 14 mA Typ

#### Logic Symbol

Vcc = Pin 16 GND = Pin 8

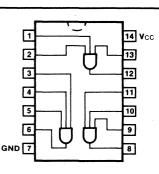

## Dual 4-Input Multiplexer

## 54F/74F352

**Description** — The 'F352 contains two inverting 4-input multiplexers with common Select inputs and separate Enable inputs. Signals applied to the Select inputs determine, within each section, which of the four data inputs is routed to the output. A HIGH signal on an Enable input forces the related output HIGH. The 'F352 is the functional equivalent of the 'F153 with inverted outputs.

Inverting Outputs

Common Select Inputs

Separate Enable Inputs

Propagation Delay 6.3 ns Typ

Supply Current 8.0 mA Typ

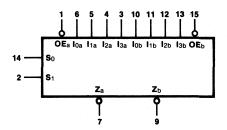

#### Logic Symbol

V<sub>CC</sub> = Pin 16 GND = Pin 8

## Dual 4-Input Multiplexer

(With 3-State Outputs)

54F/74F353

Description — The 'F353 is a dual 4-input multiplexer with inverting 3-state outputs. It selects two bits of data from any four of sources using common Select inputs. An output can be switched to the high impedance state by a HIGH signal on the respective Output Enable input. Outputs are thus capable of interfacing directly with bus oriented systems. The 'F353 is the functional equivalent of the 'F253 with inverted outputs.

Inverting 3-State Outputs Common Select Inputs Separate Enable inputs Propagation Delay 6.3 ns Typ Supply Current 13.5 mA Typ

#### **Logic Symbol**

## 1-of-10 Decoder

54F/74F537

(With 3-State Outputs)

**Description** — The 'F537 is a one-of-ten decoder/demultiplexer with four active-HIGH BCD inputs and ten mutually exclusive outputs. A polarity control input determines whether the outputs are active-LOW or active-HIGH. The 'F537 has 3-state outputs, and a HIGH signal on the Output Enable  $(\overline{OE})$  input forces all outputs to the high impedance state. Two input enables, active-HIGH E2 and active-LOW  $\overline{E}_1$ , are available for demultiplexing data to the selected output in either non-inverted or inverted form. Input codes greater than BCD nine cause all outputs to go to the inactive state (i.e., same polarity as the P input).

Output Polarity Control

Complementary Input Enables

3-State Outputs

Ignores Input Codes Above Nine

Address Delay 12 ns Typ

Enable Delay 11 ns Typ

Supply Current 44 ns Typ

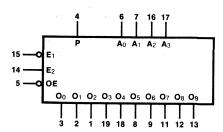

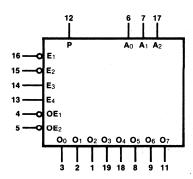

#### Logic Symbol

V<sub>CC</sub> = Pin 20 GND = Pin 10

## 1-of-8 Decoder

54F/74F538

(With 3-State Outputs)

**Description** — The 'F538 decoder/demultiplexer accepts three Address  $(A_0-A_2)$  input signals and decodes them to select one of eight mutually exclusive outputs. A polarity control input (P) determines whether the outputs are active-LOW or active-HIGH. A HIGH signal on either of the active-LOW Output Enable  $(\overline{OE})$  inputs forces all outputs to the high impedance state. Two active-HIGH and two active-LOW input enables are available for easy expansion to 1-of-32 decoding with four packages, or for data demultiplexing to one of eight or one of 16 destinations.

Output Polarity Control

Data Demultiplexing Capability

Multiple Enables for Expansion

3-State Outputs

Address Delay 12 ns Typ

Enable Delay 11 ns Typ

Supply Current 38 mA Typ

#### Logic Symbol

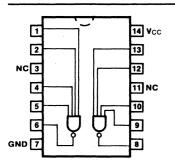

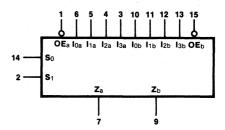

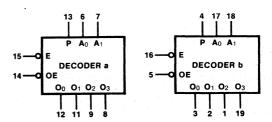

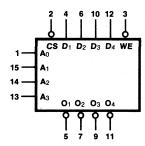

#### Dual 1-of-4 Decoder

54F/74F539

(With 3-State Outputs)

**Description** — The 'F539 contains two independent decoders. Each accepts two Address  $(A_0, A_1)$  input signals and decodes them to select one of four mutually exclusive outputs. A polarity control input (P) determines whether the outputs are active-HIGH (P=L) or active-LOW (P=H). An active-LOW input Enable  $(\overline{E})$  is available for data demultiplexing; data is routed to the selected output in non-inverted form in the active-LOW mode or in inverted form in the active-HIGH mode. A HIGH signal on the active-LOW Output Enable  $(\overline{OE})$  input forces the 3-state outputs to the high impedance state.

Two Functionally Independent Decoders

Output Polarity Control

Input Enable for Demultiplexing

3-State Outputs

Address Delay 12 ns Typ

Enable Delay 11 ns Typ

Supply Current 42 mA Typ

#### Logic Symbol

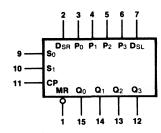

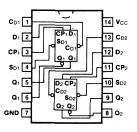

#### 4-Bit Bidirectional Universal Shift Register

#### 54F/74F194

**Description** — The 'F194 is a high speed 4-bit bidirectional shift register. Signals applied to the Select  $(S_0, S_1)$  inputs determine the mode of operation — shift left, shift right, parallel entry or hold. Except for the reset function, the 'F194 is fully synchronous and state changes are initiated by the rising edge of the clock. The flip-flops are edgetriggered and the inputs can change when the clock is in either state, provided that the recommended setup and hold times, with respect to the clock rising edge, are observed. A LOW signal on the Master Reset  $(\overline{\text{MR}})$  input overrides clocked operations and forces the outputs LOW. The circuit is useful for serial-in, serial/parallel-out or parallel-in, serial/parallel-out applications.

Serial and Parallel Entry Ports

Synchronous Serial and Parallel Operation

Fully Edge-Triggered

Asynchronous Master Reset

Shift Frequency 100 MHz Typ

Propagation Delay 7.0 ns Typ Supply Current 26 mA Typ

#### **Logic Symbol**

V<sub>CC</sub> = Pin 16 GND = Pin 8

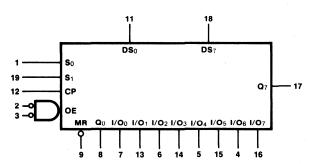

# 8-Input Universal Shift/Storage Register

(With Common Parallel I/O Pins)

54F/74F299

**Description** — The 'F299 is an 8-bit register with multiplexed 3-state I/O ports for bus oriented parallel operations and with separate serial inputs and outputs for expansion. Signals applied to the Select (S0, S1) inputs determine the mode of operation — shift left, shift right, parallel entry or hold. State changes are initiated by the rising edge of the clock. Inputs can change when the clock is in either state, provided that the recommended setup and hold times are observed, relative to the clock rising edge. An active-LOW Master Reset input overrides clocked operations and clears the register. A HIGH signal on either Output Enable  $(\overline{OE})$  input forces the I/O pins to the high impedance state but does not interfere with other operations.

Multiplexed Parallel I/O Ports Separate Serial Inputs and Outputs Expandable Bidirectional Shifting 3-State Outputs for Bus Applications Shift Frequency 80 MHz Typ Propagation Delay 9.0 ns Typ Supply Current 68 mA Typ

#### Logic Symbol

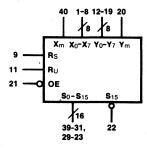

# 8-Bit Serial/Parallel Register

54F/74F322

(With Sign Extend)

Description — The 'F322 is an 8-bit shift register with provision for either serial or parallel loading and with 3-state parallel outputs plus a bi-state serial output. Parallel data inputs and parallel outputs are multiplexed to minimize pin count. State changes are initiated by the rising edge of the clock. Four synchronous modes of operation are possible: hold (store), shift right with serial entry, shift right with signal extend, and parallel load. An asynchronous Master Reset (MR) input overrides clocked operation and clears the register. A HIGH signal on the Output Enable (OE) input forces the I/O pins to the high impedance state but does not interfere with other operations. The 'F322 operates with the 'LS384 Multiplier and provides the sign extend function for twos complement arithmetic.

Multiplexed Parallel I/O Ports Separate Serial Input and Output Sign Extend Function 3-State Outputs for Bus Applications Shift Frequency 80 MHz Typ Propagation Delay 9.0 ns Typ Supply Current 70 mA Typ

# 19 3 17 S D<sub>0</sub> D<sub>1</sub> RE S/\bar{P} 18 -O OE MR 1/O7 1/O6 1/O5 1/O4 1/O3 1/O2 1/O1 1/O6 Q<sub>0</sub>

V<sub>CC</sub> = Pin 20 GND = Pin 10

#### 8-Bit Universal Shift/Storage Register

(With Synchronous Reset and Common I/O Pins)

**Description** — The 'F323 is an 8-bit universal shift/register with 3-state outputs. Its function is similar to the 'F299 with the exception of Synchronous Reset. Parallel load inputs and flip-flop outputs are multiplexed to minimize pin count. Separate inputs and outputs are provided for flip-flops Q<sub>0</sub> and Q<sub>7</sub> to allow easy cascading. Four operation modes are possible: hold (store), shift left, shift right and parallel load. The flip-flops are edge-triggered and state changes are initiated by the rising edge of the clock.

Multiplexed Parallel I/O Ports Separate Serial Inputs and Outputs Expandable Bidirectional Shifting 3-State Outputs for Bus Applications Shift Frequency 80 MHz Typ Propagation Delay 9.0 ns Typ Supply Current 66 mA Typ

#### 54F/74F323

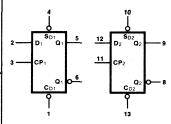

#### Quad 2-Port Register

#### 54F/74F398

**Description** — The 'F398 is the logical equivalent of a quad 2-input multiplexer feeding into four edgetriggered flip-flops. A common Select input determines which of the two 4-bit words is accepted. The selected data enters the flip-flops on the rising edge of the clock. Both the true and complement outputs of the flip-flops are available.

Select Inputs from Two Sources Fully Edge-Triggered True and Complement Outputs Propagation Delay 6.3 ns Typ Clock Frequency 150 MHz Typ Supply Current 21 mA Typ

#### **Logic Symbol**

V<sub>CC</sub> = Pin 20 GND = Pin 10

#### Quad 2-Port Register

54F/74F399

**Description** — The 'F399 is the logical equivalent of a quad 2-input multiplexer feeding into four edgetriggered flip-flops. A common Select input determines which of the two 4-bit words is accepted. The selected data enters the flip-flops on the rising edge of the clock. The 'F399 is the 16-pin version of the 'F398, with only the Q outputs of the flip-flops available.

Select Inputs from Two Sources Fully Edge-Triggered Propagation Delay 6.3 ns Typ Clock Frequency 150 MHz Typ Supply Current 21 mA Typ

#### Logic Symbol

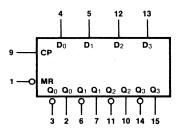

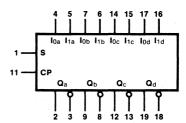

# Synchronous Presettable BCD Decade Counter

#### 54F/74F160 54F/74F162

Description — The 'F160 and 'F162 are high speed synchronous decade counters operating in the BCD (8421) sequence. They are synchronously presettable for application in programmable dividers and have two types of Count Enable inputs plus a Terminal Count output for versatility in forming synchronous multistage counters. The 'F160 has an asynchronous Master Reset input that overrides all other inputs and forces the outputs LOW. The 'F162 has a Synchronous Reset input that overrides counting and parallel loading and allows all outputs to be simultaneously reset on the rising edge of the clock.

Synchronous Counting and Loading High Speed Synchronous Expansion Propagation Delay 7.5 ns Typ Count Frequency 120 MHz Typ Supply Current 35 mA Typ

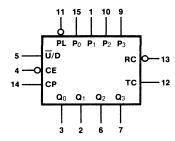

#### Logic Symbol

V<sub>CC</sub> = Pin 16 GND = Pin 8 \*MR for '160 \*SR for '162

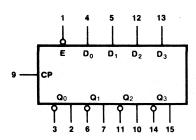

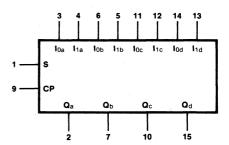

#### Synchronous Presettable Binary Counter

#### 54F/74F161 54F/74F163

Description — The 'F161 and 'F163 are high speed synchronous modulo-16 binary counters. They are synchronously presettable for application in programmable dividers and have two types of Count Enable inputs plus a Terminal Count output for versatility in forming synchronous multistage counters. The 'F161 has an asynchronous Master Reset input that overrides all other inputs and forces the outputs LOW. The 'F163 has a Synchronous Reset input that overrides counting and parallel loading and allows the outputs to be simultaneously reset on the rising edge of the clock.

Synchronous Counting and Loading High Speed Synchronous Expansion Propagation Delay 7.5 ns Typ Count Frequency 120 MHz Typ Supply Current 35 mA Typ

#### **Logic Symbol**

V<sub>CC</sub> = Pin 16 GND = Pin 8 \*MR for '161 \*SR for '163

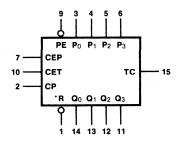

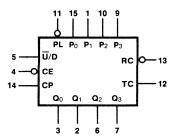

# Up/Down Decade Counter

54F/74F190

(With Preset and Ripple Clock)

Description — The 'F190 is a reversible BCD (8421) decade counter featuring synchronous counting and asynchronous presetting. The preset feature allows the 'F190 to be used in programmable dividers. The Count Enable input, the Terminal Count output and the Ripple Clock output make possible a variety of methods of implementing multistage counters. In the counting modes, state changes are initiated by the rising edge of the clock. The Count Enable and Up/Down control inputs can be changed with the clock in either state, provided only that the recommended setup and hold times are observed.

Synchronous Counting Asynchronous Parallel Load Propagation Delay 10 ns Typ Count Frequency 70 MHz Typ Supply Current 35 mA Typ

#### **Logic Symbol**

V<sub>CC</sub> = Pin 16 GND = Pin 8

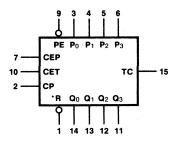

# Up/Down Binary Counter

(With Preset and Ripple Clock)

54F/74F191

Description — The 'F191 is a reversible modulo-16 binary counter featuring synchronous counting and asynchronous presetting. The preset feature allows the 'F191 to be used in programmable dividers. The Count Enable input, the Terminal Count output and the Ripple Clock output make possible a variety of methods of implementing multistage counters. In the counting modes, state changes are intiated by the rising edge of the clock. The Count Enable and Up/Down control inputs can be changed with the clock in either state, provided only that the recommended setup and hold times are observed.

Synchronous Counting Asynchronous Parallel Load Propagation Delay 10 ns Typ Count Frequency 70 MHz Typ Supply Current 35 mA Typ

#### Logic Symbol

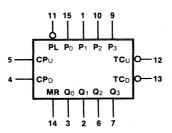

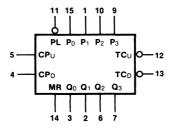

## Up/Down Decade Counter

(With Separate Up/Down Clocks)

#### 54F/74F192

Description — The 'F192 is a reversible BCD decade (8421) counter featuring synchronous counting and asynchronous parallel loading. Separate Count Up and Count Down clock inputs determine the direction of counting and in either mode the circuits operate synchronously. State changes are initiated by the rising edge of the clock. Separate Terminal Count Up (carry) and Terminal Count Down (borrow) outputs are gated clocks for a subsequent stage, thus simplifying multistage counter designs. Preset data inputs make the 'F192 useful in programmable counters. The Parallel Load (PL) input overrides counting, while the Master Reset (MR) input overrides both counting and parallel loading.

Separate Up and Down Clocks Asynchronous Parallel Loading Carry and Borrow Outputs for Cascading Propagation Delay 6.5 ns Typ Count Frequency 70 MHz Typ Supply Current 35 mA Typ

#### Logic Symbol

Vcc = Pin 16 GND = Pin 8

# Up/Down Binary Counter

(With Separate Up/Down Clocks)

54F/74F193

**Description** — The 'F193 is a reversible modulo-16 binary counter featuring synchronous counting and asynchronous parallel loading. Separate Count Up and Count Down clocks determine the direction of counting and in either mode the circuits operate synchronously. State changes are initiated by the rising edge of the clock. Separate Teminal Count Up (carry) and Terminal Count Down (borrow) outputs are gated clocks that need no external logic to serve as clocks for a subsequent stage, thus simplifying multistage counter designs. Preset data inputs make the 'F193 useful in programmable counters. The Parallel Load ( $\overline{\text{PL}}$ ) input overrides both counting and parallel loading.

Separate Up and Down Clocks Asynchronous Parallel Loading Carry and Borrow Outputs for Cascading Propagation Delay 6.5 ns Typ Count Frequency 70 MHz Typ Supply Current 35 mA Typ

#### Logic Symbol

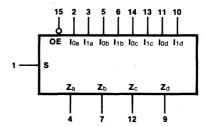

#### Octal Buffer/Line Driver 54F/74F240

(With 3-State Outputs)

Description — The 'F240 contains eight inverting buffers with 3-state outputs. They offer improved PC board density and are well suited as memory address drivers, clock drivers and bus oriented transmitters or receivers. The 'F240 has a pair of active-LOW Output Enable (OE) inputs, each of which controls four of the buffers. The data inputs are designed with Schmitt-type hysteresis to increase noise margins. Outputs are designed to exhibit low leakage in the power-down condition.

**Inverting Buffers** Separate 4-Bit Enables Output Sink 64 mA, Source 15 mA Hysteresis on Data Inputs Propagation Delay 4.5 ns Typ Supply Current 64 mA Typ

#### Logic Symbol

Vcc = Pin 20 GND = Pin 10

#### Octal Buffer/Line Driver 54F/74F241

(With 3-State Outputs)

Description — The 'F241 contains eight non-inverting buffers with 3-state outputs. Four of the buffers are controlled by an active-HIGH Output Enable (OE) input and four are controlled by an active-LOW OE input. This makes them well suited for pairing in transceiver applications. The data inputs are designed with Schmitt-type hysteresis to increase noise margins. Outputs are designed to exhibit low leakage in the power-down condition.

Non-Inverting Buffers Opposite Polarity 4-Bit Enables Outputs Sink 64 mA, Source 15 mA Hysteresis on Data Inputs Propagation Delay 6.0 ns Typ Supply Current 64 mA Typ

#### Logic Symbol

Vcc = Pin 20 GND = Pin 10

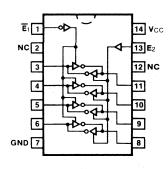

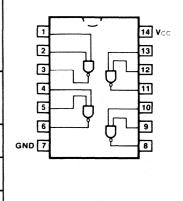

#### Quad Bus Transceiver

54F/74F242

(With 3-State Outputs)

**Description** — The 'F242 contains four inverting transceivers with 3-state outputs. They are designed for 4-line asynchronous 2-way communication between data or control busses. An active-LOW Output Enable  $(\overline{OE})$  input controls data flow in one direction; an active-HIGH OE input controls data flow in the other direction. The data inputs are designed with Schmitt-type hysteresis to increase noise margins. Outputs are designed to exhibit low leakage in the power-down condition.

Inverting Buffers

2-Way Bus Communication

Outputs Sink 64 mA, Source 15 mA

Hysteresis on Data Inputs

Propagation Delay 4.5 ns Typ

Supply Current 64 mA Typ

#### Logic Symbol

V<sub>CC</sub> = Pin 14 GND = Pin 7

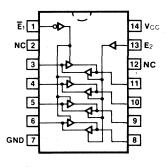

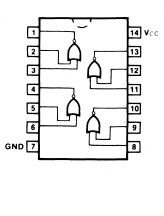

#### Quad Bus Transceiver

54F/74F243

(With 3-State Outputs)

**Description** — The 'F243 contains four non-inverting transceivers with 3-state outputs. They are designed for 4-line asynchronous 2-way communication between data or control busses. An active-LOW Output Enable  $(\overline{OE})$  input controls data flow in one direction; an active-HIGH OE input controls data flow in the other direction. The data inputs are designed with Schmitt-type hysteresis to increase noise margins. Outputs are designed to exhibit low leakage in the power-down condition.

Non-Inverting Buffers

2-Way Bus Communication

Outputs Sink 64 mA, Source 15 mA

Hysteresis on Data Inputs

Propagation Delay 6.0 ns Typ

Supply Current 64 mA Typ

#### Logic Symbol

#### Octal Buffer/Line Driver 54F/74F244

(With 3-State Outputs)

Description — The 'F244 contains eight non-inverting buffers with 3-state outputs. They offer improved PC board density and are well suited as memory address drivers, clock drivers and bus oriented transmitters or receivers. The 'F244 has a pair of active-LOW Output Enable (OE) inputs, each of which controls four of the buffers. The data inputs are designed with Schmitt-type hysteresis to increase noise margins. Outputs are designed to exhibit low leakage in the power-down condition.

**Non-Inverting Buffers** Separate 4-Bit Enables Outputs Sink 64 mA, Source 15 mA **Hysteresis on Data Inputs** Propagation Delay 6.0 ns Typ Supply Current 64 mA Typ

#### **Logic Symbol**

Vcc = Pin 20 GND = Pin 10

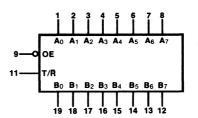

#### Octal Bidirectional Transceiver

54F/74F545

(With 3-State Inputs/Outputs)

Description — The 'F545 contains eight non-inverting bidirectional buffers with 3-state outputs and is intended for bus-oriented applications. Current sinking capability is 20 mA at the A ports and 64 mA at the B ports. The Transmit/Receive (T/R) input determines the direction of data flow through the bidirectional transceiver. Transmit (active-HIGH) enables data from A ports to B ports; Receive (active-LOW) enables data from B ports to A ports. The Output Enable input, when HIGH, disables both A and B ports by placing them in a 3-state condition. Output HIGH voltage VoH is specified as 3.6 V for MOS interfacing.

**Non-Inverting Buffers Bidirectional Data Path** B Outputs Sink 64 mA, Source 15 mA VOH Specified as 3.6 V at 0.4 mA Propagation Delay 6.0 ns Typ Supply Current 128 mA Typ

#### **Logic Symbol**

Vcc = Pin 20 GND = Pin 10

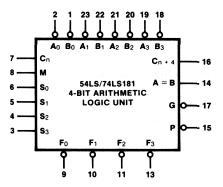

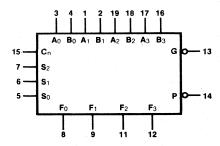

# 4-Bit Arithmetic Logic Unit

#### 54F/74F181

**Description** — The 'F181 is a 4-bit Arithmetic Logic Unit capable of performing 16 arithmetic or 16 logic operations on two 4-bit operands  $A_0 - A_3$  and  $B_0 - B_3$ . The Carry Out  $(C_{n+4})$  output is provided for ripple carry expansion, while the Carry Propagate  $(\overline{P})$  and Carry Generate  $(\overline{G})$  outputs can be used with an 'F182 or similar Carry Lookahead Generators for faster operations on longer words. The Mode Control (M) input determines whether a logic (M=H) or an arithmetic (M=L) operation is performed. Signals applied to the Select  $(S_0 - S_3)$  inputs determine the specific function or operation.

Performs 16 Arithmetic Operations

Performs 16 Logic Functions

Internal Lookahead for Fast Ripple Carry

G and P Outputs for External Lookahead

A or B to Carry Delay 10 ns Typ

Ex-OR Logic Delay 8.7 ns Typ

Supply Current 39 mA Typ

#### Logic Symbol

Vcc = Pin 24 GND = Pin 12

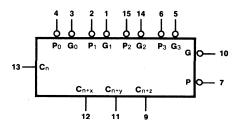

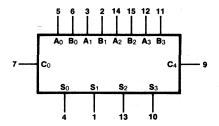

#### Carry Lookahead Generator

#### 54F/74F182

**Description** — The 'F182 is a high-speed carry lookahead generator for use with the 'F181, 'F381, 2901A or other 4-bit ALUs in arithmetic operations on words longer than four bits. It accepts up to four pairs of active-LOW Carry Propagate ( $\overline{P}_0 - \overline{P}_3$ ) and Carry Generate ( $\overline{G}_0 - \overline{G}_3$ ) signals, an active-HIGH Carry input ( $C_n$ ) and provides anticipated active-HIGH carries ( $C_n + x$ ,  $C_n + y$ ,  $C_n + z$ ) across four ALUs. It also has active-LOW Carry Propagate ( $\overline{P}$ ) and Carry Generate ( $\overline{G}$ ) outputs for optional use in further levels of lookahead. The 'F182 works equally well when the ALU operand inputs follow either the active-LOW or the active-HIGH convention.

Provides Lookahead Across Four ALUs Multi-Level Capability for Longer Words Less Loading of ALU Outputs Propagation Delay 4.6 ns Typ Supply Current 19 mA Typ

#### Logic Symbol

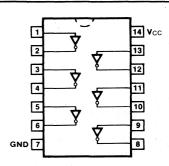

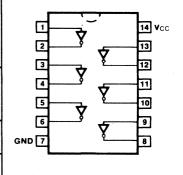

### 9-Bit Parity Generator/Checker

#### 54F/74F280

Description — The 'F280 is a high-speed parity generator/checker that accepts nine bits of input data and detects whether the number of HIGH inputs is even or odd. If even, the Sum Even output is HIGH; if odd, the Sum Even output is LOW. The Sum Odd output is the complement of the Sum Even output. For longer words, the Sum Even output is used as an input to the next package.

Nine Input Lines Odd or Even Parity Propagation Delay 12.5 ns Typ Supply Current 25 mA Typ

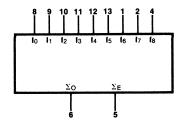

#### **Logic Symbol**

V<sub>CC</sub> = Pin 14 GND = Pin 7

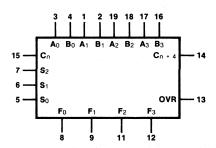

# 4-Bit Binary Full Adder

(With Fast Carry)

54F/74F283

**Description** — The 'F283 high-speed 4-bit binary full adder with internal carry lookahead accepts two 4-bit binary words  $(A_0-A_3,\,B_0-B_3)$  and a Carry input  $(C_0)$ . It generates the binary Sum outputs  $(S_0-S_3)$  and the Carry output  $(C_4)$  from the most significant bit. The 'F283 will operate with either active-HIGH or active-LOW operands (positive or negative logic).

Adds Two 4-Bit Numbers

Full Internal Carry Lookahead

Fast Ripple Carry for Economical Expansion

Ripple Carry Delay 4.7 ns Typ